# TAME:

## **Trusted and Assured MicroElectronics**

Working Groups Report

December 2019

The TAME Steering Committee would like to express their deepest gratitude to all volunteers for their hard work in the three committees over the past 18 months to develop these reports. The volunteers have been acknowledged at the beginning of each report.

Mark Tehranipoor University of Florida

Waleed Khalil Ohio State University

Matt Casto OSD

**Yousef Iskander** Cisco

Brian Dupaix Air Force Research Laboratory (AFRL)

**Ro Cammarota** Intel

**Brian Cohen** Institute of Defense Analysis (IDA)

### **Table of Contents**

| $Chapter \ 1: Hardware \ Assurance \ and \ Weakness \ Collaboration \ and \ Sharing \ (HAWCS) \ .$ | 1  |

|----------------------------------------------------------------------------------------------------|----|

| 1.1 Problem Statement                                                                              | 1  |

| 1.2 Objectives                                                                                     | 4  |

| 1.3 HAWCS Development Areas                                                                        | 6  |

| 1.4 Conclusion and Future Directions                                                               | 24 |

| References                                                                                         | 26 |

## Chapter 2: Design for Security 29 2 1 Problem Statement 29

| 2.1 Hobiem Statement                                | 29 |

|-----------------------------------------------------|----|

| 2.2 Security Challenges in Current Microelectronics |    |

| 2.3 Security Definitions                            | 32 |

| 2.4 Security Metrics                                | 36 |

| 2.5 Usage Model                                     | 39 |

| 2.6 Future Directions                               | 41 |

| References                                          | 42 |

| Chapter 3: Microlectronics Secuity and Trust - Grand Challenges | 44 |

|-----------------------------------------------------------------|----|

| 3.1 Problem Statement                                           | 44 |

| 3.2 Objectives                                                  |    |

| 3.3 Major Challenges                                            | 44 |

| References                                                      |    |

## Chapter 1: Hardware Assurance and Weakness Collaboration and Sharing (HAWCS)

#### **Contributors:**

- Jeremy Bellay (Lead)

- Domenic Forte (Scribe)

- Bob Martin (Advisor)

- Jon Boyens (Advisor)

- Mike Borza

- Ron Perez

- Yatin Hoskote

- Sandip Ray

- Ioannis Savidis

- Fareena Saqib

- Whitney Batchelor

- Lisa McIlrath

- Khalil Maalouf

- Mark Temmen

- Marion Williams

- Vivian Kammler

- Melanie Berg

- Vikram Rao

- Wayne Reed

#### **1.1 Problem Statement**

Battelle University of Florida MITRE NIST **Synopsys** Intel ARM University of Florida **Drexel University UNC** Charlotte **Graf Research** University of Florida **Riverside Research** U.S. Army **NIMBIS Services** Sandia National Labs NASA Aerospace Honeywell

The field of computer and communications security has traditionally viewed hardware as an immutable root-of-trust. However, the last decade of hardware security research has led to the discovery of hardware-oriented weaknesses that can be exploited remotely, in the supply chain, through physical access, or through any combination of the three.

In particular, 2018 was a catastrophic year for many of the top processor vendors. Researchers uncovered multiple CPU hardware vulnerabilities – Meltdown, Spectre, Foreshadow, and even a new variant of Rowhammer to name a few [1]–[4] – and showed how they could be used to gain access to forbidden data and system privileges, even in trusted execution environments. Most exploits were 'baked into' the processor architectures through performance enhancing features such as branch prediction, speculative execution, and translation lookaside buffer. By and large, these vulnerabilities were complicated to mitigate and incurred significant performance degradation as well as other unintended side effects [5]. Those that could not be addressed by patches shall require system replacement.

In parallel, concerns are mounting about firmware and hardware-level attacks occurring in the supply chain. Semiconductor globalization has benefitted the industry by shortening time-to-market, lowering non-recurring engineering costs, and managing the escalating investment

required to build state-of-the-art integrated circuit (IC) manufacturing facilities and the years it takes them to achieve a high-yield level of production, but not without creating its share of new problems. In 2008, an IEEE Spectrum article [6] underscored the risks of electronic backdoors (i.e., hardware Trojans) inserted by contract foundries and third party intellectual property (IP) vendors. Further, supply chain interdiction, where items such as routers, flash drives, and other electronic devices are compromised while in transit to their final destination [7], has also been reported. Recently, there has been an increase in public awareness around the potential of deliberate backdoors in hardware including the (heavily disputed) "Big Hack" article published by Bloomberg [8], and the controversy surrounding Huawei's primary role in 5G hardware. Last but not least, counterfeit electronics are a longstanding threat that have only become worse with the increase in global e-waste [9], long-lived systems, and chip obsolescence[10].

Beyond simply offering an alternative attack surface beyond software, hardware has other attractions to attackers that will make it an increasingly common target. Since hardware is the foundation of computing and operates at the lowest abstraction layer, common software mitigations such as system updates and patches are inadequate. Moreover, while hardware attacks require physical access and have long been considered too expensive, the landscape is starting to change in the attacker's favor. As part of the emerging internet of things (IoT), the number of "smart things" is soon expected to dwarf mobile computing devices[11]. IoT products are often deployed in hostile environments where they can operate for years with minimal intervention. Those still practicing lax security practices (hard-coded cryptographic keys, unprotected JTAG, etc.) are in for an unpleasant surprise. In addition, improvements in the capabilities of failure analysis tools, especially semi-invasive ones, coupled with lower barriers to their access make on-chip assets, secrets, and IP more vulnerable to fault injection, probing, and reverse engineering than ever before[12].

We follow MITRE's definitions of vulnerabilities and weaknesses [1]: A vulnerability is an error in a particular information system that may allow exploitation of that system. Weaknesses, on the other hand, are the circumstances in design and manufacture that allow for the existence of a vulnerability. Extending MITRE's definitions to hardware, we define a hardware vulnerability/ weakness as one existing in the hardware or firmware of a system. Perhaps a functional definition is that the vulnerability or weakness can be potentially mitigated but not removed by a software changes.

Hardware is also evolving rapidly, and thus creating fundamentally new attack surfaces, many of which will probably never be entirely secured. The pressure of increasing performance and compactness in the face of a presumed physical limit on node size has led to new creative approaches that have increased performance but also opened new attack surfaces; both Rowhammer and Spectre/Meltdown can be seen to represent not individual vulnerabilities but entire attack surfaces. Several new technologies are promised in the next 10-20 years including 5nm and below node sizes, neuromorphic computing, Carbon-Nanotube FET, and quantum computing bringing with them unforeseen weaknesses.

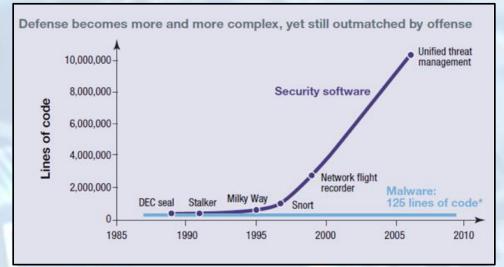

Left unaddressed, vulnerabilities expose critical systems, their information, and the people who rely on them. But in order to be fixed, they must first be identified. The rise of viruses, malware, and remote attacks in the 80's, 90's, and early 2000's led to efforts aimed at supporting and

coordinating vulnerability education, discovery, advisories, and alleviation. These included a common language and taxonomies to describe software and software-related weaknesses [13], attack patterns [14], and vulnerabilities [15], [16], avenues for responsible disclosure of vulnerabilities and exposures [16], [17], entities to coordinate responses between researchers, vendors, and deployers, and approaches to prioritize mitigations [18].

Unfortunately, the unique challenges faced by semiconductor companies make it impractical to extend the above frameworks and management techniques in their entirety directly to hardware because hardware vulnerabilities differ in nature to their software counterparts. Current software vulnerability disclosure policies advise up to 90 days to develop and distribute a patch before public disclosure, but experience shows that mitigation of hardware vulnerabilities requires more time. This is because semiconductor companies need to work with companies across their supply chain to understand the implications of vulnerabilities and possible solutions at multiple levels – from IC to microcode to software. Patches must also be well-tested in order to maintain operation across diverse environments encountered by the chip; otherwise, serious performance and stability issues can arise from the patch. For critical real-time systems, which have already undergone years of certification, this is unacceptable. Sometimes, a costly hardware recall is the only solution. Beyond cost, however, tracking down the hardware assets of affected customers is so cumbersome that many vulnerable systems are likely to remain in the wild.

For these reasons, those who discover hardware vulnerabilities are often discouraged from publicly sharing their findings [19]. A similar attitude of squelching discussion about security vulnerabilities existed in the software arena in the late 90's, supposedly to protect the public interest by withholding critical information from attackers and to safeguard vendor reputation, and threats of lawsuits were prevalent. On the other hand, some consider the discouragement of sharing security research findings to be counterproductive. For software, and even more so hardware, prevention is likely less expensive and far more effective than mitigation. By allowing a community of researchers and practitioners to more openly discuss and share understandings about the problems that make hardware vulnerable, how to avoid, prevent, or recognize them before they make it into hardware implementations, etc., the entire ecosystem benefits. Lessons learned and best practices are needed so that the community can train design engineers and develop robust, tools and practices that can identify the weaknesses leading vulnerabilities and prevent their introduction and reoccurrences. Instead, it is more common today for fragile tools and checking regimes to be developed in-house, leaving external community of design engineers in the dark and destined to repeat the same mistakes in the systems of other vendors.

In summary, hardware weaknesses and vulnerabilities are a growing concern but the most effective way to deal with them is still an open problem. While one can look at past experience in software, there needs to be a candid discussion within the entire hardware community about how to properly balance the tradeoffs of disclosure on the technology ecosystem as well as society.

#### **1.2 Objectives**

The Trusted and Assured MicroElectronics (TAME) Forum's "Hardware Vulnerability Database" (HVD) working group was initially created to provide a roadmap for community dialogue and first steps towards investigation of these issues. While the working group's original focus (and therefore name) was on the creation of a HVD, it eventually become clear that the technologies

used to effectively characterize and share information regarding hardware vulnerabilities is inherently valuable to the community as well. Thus, the group also focused on the issues and technologies for effective sharing of information about the identification and prevention of hardware vulnerabilities, and its name was changed to "Hardware Assurance and Weakness Collaboration and Sharing" (HAWCS).

The real and perceived risks associated with hardware vulnerability sharing and disclosure necessitate a collaborative community effort in the development of effective common characterization, identification, and sharing schemes. The TAME HAWCS working group has representation from industry, government, and academia. This diversity allows the group to pursue three primary goals: First, it allows the identification of risks and benefits to the different sets of stakeholders; an oft cited hurdle to sharing hardware vulnerability details has been the perceived risk associated with vulnerability disclosure and the lack of quantifiable reward. Second, each community offers unique insight and perspective essential to the development of a common identification of vulnerabilities and the development of a common characterization of the underlying physical processes. Finally, the diversity of the working group allots for the integration and dissemination of information across the relevant communities; previous efforts have been limited by the difficulties of communication between groups of stakeholders.

The HAWCS working group has decided to address the following issues through its multidisciplinary and multi-party perspective:

**Identification of current vulnerability reporting and assessment structures.** There are numerous ongoing efforts related to the characterization, storage, and reporting of hardware vulnerabilities. The most notable is the software security ecosystem that includes notable components such as Common Vulnerabilities and Exposures (CVE), the National Vulnerability Database (NVD), and agreed upon methods of responsible disclosure. However, there are other relevant efforts such as the Society for Automotive Engineers' Test Methods Standard [20], and the Accellera Systems Initiative[21][21][15]. The HAWCS working group has surveyed the current vulnerability sharing efforts and shall summarize their relevance to hardware vulnerabilities in this report.

**Survey benefits and risk to stakeholders.** The active participation of all three stakeholder groups – government, industry and academia -- is essential for the success of any vulnerability sharing scheme. The working group is leveraging the diversity of its members to identify the risks and benefits associated with a sharing hardware vulnerability information. This will help ensure that future efforts are meaningful to the participants and avoid exposure to unnecessary risks. Importantly, we anticipate that a shared vulnerability characterization scheme will help structure vulnerability comparison and discovery even for parties that are otherwise non-communicative with the rest of the community.

**Survey of hardware security topics.** There are many topics relevant to hardware security. The TAME HAWCS working group intends to use the breadth the participants' expertise to survey all the security and reliability concerns of each group member. While some concerns may not be of interest to all stakeholders, the underlying mechanism of the vulnerability (and its detection) may be relevant. For example, while industry may consider the risk of hardware Trojans to be relatively

low, tools developed for Trojan detection (e.g., side channel analysis) may offer inexpensive detection of information leakage and counterfeits.

**Knowledge structures for vulnerability characterization.** Knowledge structures used to characterize vulnerabilities are a key aspect to leveraging knowledge about vulnerabilities across the community. Even when specific vulnerabilities are not shared due to their sensitive nature, controlled characterization languages such as ontologies can be used to describe the mechanism of a class of vulnerabilities at a shareable, higher level of abstraction. Additionally, shared description languages can be used to describe best practices to avoid vulnerabilities. The development of such knowledge structures has been recognized as valuable even without a shared database as it facilitates communication about unshared vulnerabilities and can be used by parties to structure their own vulnerability cataloging efforts. Finally, a well-structured characterization that links vulnerabilities to their underlying mechanism is essential for the use of analytical methods to detect new vulnerabilities and predict their occurrence in design. A goal of the working group is to investigate what knowledge structures are available for the description of hardware vulnerabilities (e.g., CVE, CWE, CAPEC etc.), and how they need to be extended to describe the often physical nature of hardware vulnerabilities, as well as supporting and referencing the necessary data structures.

**Integration with ongoing and future projects.** In addition to surveying the current and ongoing efforts touching hardware vulnerabilities, the working group is considering how to best integrate and provide value to these ongoing efforts. The working group is already aware of several ongoing efforts including the CVE/NVD ecosystem, Accellera's standards creation efforts, and the efforts by the Society for Automotive Engineers. However, we anticipate the application of working group output to go beyond active collaborators. For example, a government agency may keep a database of vulnerabilities which is too sensitive for even highly controlled sharing between industry partners. However, external organizations may be able to benefit from the standards and ontology used in the highly sensitive database. The working group members will leverage their connections across different stakeholder groups to support these separate initiatives that are important for hardware security even if their sensitivity discourages active participation in a larger community.

**Models for long term funding and sustainment.** A key aspect of efforts around an HVD and ontology efforts is ensuring that the initial development is followed by indefinite sustainability. A key danger associated with any kind of knowledge structure development is rapid obsolescence. The working group plans to identify interested partners capable of funding early research and development of vulnerability sharing resources. While funding is always a key issue, leveraging the open source community for the maintenance and expansion of HVD resources must also be explored. Finally, we must also identify potential long term sustainment models such as subscriptions, incorporation into current government programs and support via consortium.

This report, which shall discuss the above topics in more detail, was developed in the multiple phases. This outline was prepared, presented, and discussed at the November 2018 TAME meeting in Columbus, Ohio. The initial draft was compiled and presented at the May 2019 TAME meeting at HOST 2019 in McLean, VA. The final draft was compiled for the TAME forum meeting December 2019 in Gainesville, FL. The final report will be published in Hardware and Systems Security (HaSS) Journal.

#### **1.3 HAWCS Development Areas**

#### **1.3.1 Risks and Benefits to Stakeholders**

#### 1.3.1.1 Industry

Risks:

- 1. *IP disclosure*: Hardware weakness characterization could benefit from realistic test articles from industry, but industry stakeholders are very protective of their hardware IP and would be unwilling to divulge it, even for perceived public good. Disclosing details of vulnerabilities in a public database could give potential attackers hints for exploiting additional weaknesses that have not yet been discovered. Disclosures may also be less useful without explanation of design details that are proprietary.

- 2. *Premature vulnerability dissemination*: If a vulnerability becomes public through the HVD before patches or other mitigations have been deployed, the IP/system vendors could incur significant costs and other losses due to negative publicity and legal liabilities from system downtime and theft/corruption of customer data.

- 3. *Reputational damage*: By putting sensitive information in the public sphere before the details and extent of its impact has been fully analyzed, companies run the risk of being caught in embarrassing scenarios which could result in significant damage to their brand and reputation. For example, incomplete analysis may lead to attributing cause and responsibility incorrectly. Once reputational damage is done, it can be hard to undo.

#### Benefits:

- 1. *Standardization:* Use of a common language and taxonomy to communicate about hardware vulnerabilities would reduce the chance of misunderstanding and make engagements much more productive.

- 2. *Baseline:* Use the database as a baseline for internal security due diligence on all products before release. One could also use the database as the basis for threat modeling in implementation of a secure development lifecycle for products. There is no coverage metric for robustness. The database could be used as a proxy for a coverage metric.

- 3. *Collaboration:* A mechanism that facilitates sharing of information confidentially between stakeholders would enable responses to newly discovered vulnerabilities to be faster and more coordinated.

- 4. *Supply chain robustness:* Could potentially use certification against the database as a certificate of trust between suppliers and procurement departments to build a more robust supply chain.

- 5. *Tool development:* Provide a target database for development of electronic design automation (EDA) tools for finding vulnerabilities and for validating effectiveness of mitigations. Tools would be especially useful in verifying effectiveness of mitigations.

- 6. *Education and training:* Database can be used in universities for training new grads, as well as for training security engineers in industry.

- 7. *Severity metrics:* The database could be enhanced with additional information like severity metrics to help prioritize vulnerabilities and modulate the resources assigned to combat them. For example, a common understanding of the severity metrics would help IP providers and IP integrators to level set expectations on mitigation responsibilities.

- 8. *Mitigations:* The database could also include mitigations where possible, without divulging confidential information, to help the community respond more rapidly to known vulnerabilities.

#### 1.3.1.2 Government

The risks and benefits of sharing technologies are similar for government and for industry. The major risks being the unintentional disclosure of IP and the weaponization of disclosed vulnerabilities. In addition, government is burdened with legacy devices that may contain hard to mitigate vulnerabilities that have been effectively dealt with in private industry. Additionally, other nation states are willing to spend the resources to develop hard to reach exploits to access government targets. On the other hand, the government has many siloed databases of known vulnerabilities and programs to investigate potential weaknesses. Public sharing technologies can aid these otherwise isolated efforts by providing external fodder and internal structure

#### Risks:

- 1. Exposure of vulnerabilities in legacy devices Government maintains some systems long after their components have exited the commercial market. Thus even "obsolete" shared vulnerabilities may still pose a risk to government systems.

- 2. Exploitation of sophisticated vulnerabilities There are many vulnerabilities that take high effort and expertise to exploit, which make them less tempting targets for monetarily motivated crimes. However, adversary nation states have the expertise and resources to exploit these vulnerabilities so as to subvert specific otherwise hardened targets.

#### Benefits:

- 1. Standardization in siloed data centers -- The development of vulnerability description and sharing technologies will benefit stakeholders within government agencies that possess unshareable vulnerability databases.

- 2. Defense strategies at the level of weaknesses Government specific electronics are extensively red-teamed and databases of even abstract weaknesses can help red teams design realistic testing strategies.

#### 1.3.1.3 Academia

#### Risks:

Academic researchers are bound to uphold their university mission statements which often involve "promoting the common good". However, the dual nature of security research makes this unwieldy. On the one hand, the public has the right to know about serious issues in the products they buy. Further, in the hands of vendors, this information is almost guaranteed to result in better products. On the other hand, the same information can be exploited by criminals and unethical hackers. Researchers are often left with two choices. Avoid applied research, and, subsequently, access to the vast amount of funding in this space. Or participate and be bound by ambiguous laws and protocols surrounding proper disclosure of information. For the second route, risks include:

- 1) *Legal threats and lawsuits:* Even in the case of proper disclosure, the inconsistency in handling disclosures between organizations combined with the open-ended interpretation of existing laws (e.g., definition of "good-faith" research) sometimes results in legal issues for ethical researchers working to improve security.

- 2) Loss of academic licenses and donation programs: Universities are reliant on access to commercial tools and products for education and research purposes. Even when lawsuits are not pursued against a researcher, organizations are still within their right to deny these resources to the researcher's institution, which can seriously harm their ability to deliver on existing projects, pursue research funding, and place students in the job market.

- 3) Prolonged publication delays: After proper disclose, embargoes are often used to ensure that there is enough time for the affected company to provide effective workarounds. However, the indeterminate timescale by which hardware vulnerabilities are resolved could result in significant publication delays for the discoverer. University researchers are under immense pressure to disseminate artifacts of their work in high-impact venues. Competition for research funding is fiercer than ever today, and publication is vital to the advancement of academic careers and the pursuit of research funding. By agreeing to an embargo, a researcher could risk proper recognition and rewards if a less ethical research group circumvents disclosure and prematurely disseminates the same vulnerability.

#### Benefits:

Similar benefits to industry, especially *Standardization*, *Collaboration*, and *Education and training*. In addition, academics would benefit from a more welcoming environment where the disclosure/mitigation process is less ambiguous and less treacherous.

#### **1.3.2** Limitations of Existing Ecosystem and Integration with a HVD

The idea of a public national hardware vulnerability database is fairly new and comes two decades after the establishment of a public national vulnerability database that was initially focused on software issues. For context, in the late 1990's there was a rich and thriving set of groups trying to discuss and share information surrounding software vulnerabilities, how they occurred, how they were attacked, how to recognize them, what to do about them, and how to prioritize them. While thriving, these ecosystems were disjointed, duplicative, convoluted to use, and had no correlations amongst or between them. Against this backdrop, the MITRE Corporation, a not-for-profit corporation that runs Federally Funded Research and Development Centers (FFRDCs) for multiple<sup>[1]</sup> departments of the US Government, came up with the idea of a Common Enumeration of Vulnerabilities and presented a paper with that title<sup>[2]</sup> at the University of Purdue's 2nd Workshop on Research with Security Vulnerability Databases in January of 1999 to a mixed audience of industry, government, and academia. While there was immediate argument about what constituted a vulnerability, there was no disagreement on the potential simplification and communication improvements a simple correlation identifier could bring to the vulnerability communities.

Years after its September 1999 launch of CVE, the need for common terminology about what weaknesses in software created those vulnerabilities and how they could be attacked led MITRE

<sup>&</sup>lt;sup>1</sup> MITRE – We Operate FFRDCs, MITRE, https://www.mitre.org/centers/we-operate-ffrdcs

<sup>&</sup>lt;sup>2</sup> Towards a Common Enumeration of Vulnerabilities, MITRE, http://cve.mitre.org/docs/docs-2000/cerias.html

to launch the Common Weakness Enumeration and the Common Attack Pattern Enumeration and Classification efforts and NIST to establish the National Vulnerability Database[<sup>3</sup>].

#### **1.3.2.1** Common Vulnerabilities and Exposures (CVE®)

The CVE website provides a publicly available dictionary of publicly known vulnerabilities in commercial and open source software that helps individuals and organizations correlate the numerous types of public and private information about such public vulnerabilities in applications and other cyber-enabled capabilities. The dictionary is organized in an intuitive manner based on known vantage points and abides by a concise schema for describing related public information and offering a mechanism for the correlating the shared information about them. CVE's origin is based on the concept of a simple agreed upon list of identifiers for publicly known vulnerabilities to help correlate those pieces that are referring to or discussing the same public issue [22].

**CVE entries or CVEs** are a publicly known issues that need to be patched or mitigated to address an exploitable vulnerability. CVEs are created through CVE Naming Authorities (CNAs) that represent a web of organizations sharing the responsibilities of consistently associating CVE identifiers with security issues. While MITRE is currently the root CNA, and CNA of last resort, there are nearly 100 other organizations that constitute security researchers, have specific products, product types, or other specified domains for which they have been identified as the preferred CNA which the community should work with to assign CVE identifiers. A CNA of last resort is a role where, if for some reason the CNA that should be involved with assigning a CVE for an issue cannot be reached or is not responsive, the party trying to coordinate a new vulnerability can go to the CNA of last resort and work with them to get the CVE.

A **vulnerability** is a specific type of weakness or weaknesses in a product that is exploitable by a threat. Specific vulnerabilities are concrete examples of items (hopefully) described in the catalog of Common Weakness Enumeration (CWE) items and attackable by the attack patterns captured in the Common Attack Pattern Enumeration and Classification (CAPEC) collection. By linking a public vulnerability in a specific product to the weakness and attack pattern collections, organizations can leverage those collections and the information in them in their assessment and investigation into newly discovered examples of vulnerabilities and also offer opportunities to examine their own code collections for the same type of vulnerability.

#### **1.3.2.2** Common Weakness Enumeration (CWE<sup>TM</sup>)

The CWE website provides a publicly available catalog of the weaknesses that occur in the software architecture, design, code, or deployment of the software that can result in exploitable vulnerabilities and is meant to help individuals and organizations understand how these weaknesses in applications and other cyber-enabled capabilities occur. The catalog of weaknesses is organized in an intuitive manner based on known vantage points and abides by a comprehensive schema for describing related information about the weaknesses and sharing information about them. CWE's origin is derived from working with the real-world examples of the types of vulnerabilities that appear in software applications and meant to generalize those real-world flaws into conceptual patterns of what make software exploitable so that people can learn to recognize

<sup>&</sup>lt;sup>3</sup> A Framework for Modeling the Software Assurance Ecosystem: Insights from the Software Assurance Landscape Project, SEI, https://apps.dtic.mil/dtic/tr/fulltext/u2/a528427.pdf

them early in the lifecycle of the software and either avoid introducing them or finding them quickly and addressing them before the software is put into operation.

**CWE entries or CWEs** are a mixture of types of vulnerabilities found by exploiting them "in the wild" or through examination and testing of software by hackers, developers, and testers. CWEs are created by generalizing a specific vulnerability in a particular product or through examination of the architecture, design, code, or deployed software and finding constructs that allow someone to do something that was not intended.

A **weakness** is a description of the common attributes and susceptibilities of an architecture, design, code, or deployment construct that allows an adversary to exploit the weaknesses in cyberenabled capabilities. Weaknesses define the opportunities that an adversary may leverage and how the builder/defender can go about finding and removing them. If an organization is concerned with specific weaknesses because of the possible consequences from a successful attack on them, the relationships between CWEs and CAPECs can be used to identify the likely CAPECs for a CWE and that knowledge can inform the defender on options for defense.

The following is a list of the properties of weaknesses in CWE. For definitions of each of these properties see <u>https://cwe.mitre.org/documents/glossary/index.html</u>.

- Description

- Extended Description

- Alternate Terms

- Background Details

- Modes of Introduction

- Applicable Platforms

- Common Consequences

- Likelihood of Exploit

- Observed Examples

- Potential Mitigations

- Detection Methods

- Memberships

#### **1.3.2.3** Common Attack Pattern Enumeration and Classification (CAPEC<sup>TM</sup>)

The CAPEC website provides a publicly available catalog of common attack patterns that helps individuals and organizations understand how adversaries exploit weaknesses in applications and other cyber-enabled capabilities. The catalog is organized in an intuitive manner based on known vantage points and abides by a comprehensive schema for describing related attacks and sharing information about them. CAPEC's origin is based on the concept of software design patterns – templates for the design and implementation of commonly used software techniques.

**CAPEC entries or CAPECs** are a mixture of attack patterns actively seen "in the wild", through proof-of-concept, or based on research surrounding what is theoretically possible to do. CAPECs are created by generalizing adversary behaviors and can be thought of as an extrapolation of things that could happen or be observed. For instance, how does an adversary take advantage of a software weakness – what are the steps taken, what is the knowledge needed to follow those steps, how difficult is it to achieve, how likely is success? These are the types of questions that CAPEC aims to answer.

An **attack pattern** is a description of the common attributes and approaches employed by adversaries to exploit known weaknesses in cyber-enabled capabilities. Attack patterns define the challenges that an adversary may face and how they go about solving them. They derive from the concept of design patterns applied in a destructive rather than constructive context and are generated from in-depth analysis of specific real-world exploit examples, research, and

- Notes

- Taxonomy Mappings

- Related Attack Patterns

- References

technologies. If an organization is concerned with attacks on specific weaknesses because of the possible consequences, the relationships between CWEs and CAPECs can be used to identify the likely CAPECs for a CWE and that knowledge can inform the defender on options for defense.

The following is a list of the properties of attack patterns in CAPEC. For definitions of each of these properties see <u>https://capec.mitre.org/documents/schema/index.html</u>.

- Description

- Alternate Terms

- Likelihood of Attack

- Typical Severity

- Related Attack Patterns

- Execution Flow

- Prerequisites

- Skills Required

- Resources Required

- Indicators

- Consequences

- Mitigations

**Mechanisms of Attack**. The high level categories of CAPEC attack patterns are organized by the mechanisms of attack:

| • Engage in Deceptive<br>Interactions | Manipulate System Resources | • Manipulate Timing and State       |

|---------------------------------------|-----------------------------|-------------------------------------|

| • Abuse Existing Functionality        | • Inject Unexpected Items   | Collect and Analyze     Information |

| Manipulate Data Structures            | Employ Probabilistic        | Subvert Access Control              |

Manipulate Data Structures

Employ Probabilistic

Sub Techniques

These categories are not organized around the goals or consequences of an attack pattern, but the steps necessary to performing an attack. The important aspect of the pattern is "how" to achieve the goal. The pattern may be used to cause many different consequences, but the steps are relatively constant.

**Domains of Attack.** A second view is available related to the different domains where attack patterns are relevant.

Communications

- Software

- Hardware

- Supply Chain Physical Security

Social Engineering

Software developers can use this view to become aware of relevant attack patterns and can design and implement their software to make it more difficult to put these attack patterns into practice, thereby reducing their application's risk surface.

The Domain of Attack view also showcases attack patterns related to social engineering, supply chain, and physical attacks. Social Engineering CAPECS reveal many non-technical means by which adversaries act on their objectives. The list of Supply Chain CAPECS illustrate how the long chain of parts/processes that make up the final piece of hardware/software can be attacked at various points along the way and the specific weaknesses that are leveraged in such attacks need to be captured and shared across those communities. CAPECs related to physical security can assist those needing to know the various ways their physical facilities, devices, and locations can be breached.

- Related Weaknesses Taxonomy Mappings

- References

• Example Instances

#### **1.3.2.4 CMU CERT/CC**

The CERT Coordination Center (CERT/CC) is the coordination center of the computer emergency response team (CERT) for the Software Engineering Institute (SEI), a non-profit United States FFRDC. The CERT/CC researches software bugs that impact software and internet security, publishes research and information on its findings, and works with business and government to improve security of software and the internet as a whole.

The CERT/CC works directly with software vendors in the private sector as well as government agencies to address software vulnerabilities and provide fixes to the public. This process is known as coordination. The CERT/CC promotes a particular process of coordination known as *Responsible Coordinated Disclosure*. In this case, the CERT/CC works privately with the vendor to address the vulnerability before a public report is published, usually jointly with the vendor's own security advisory. In extreme cases when the vendor is unwilling to resolve the issue or cannot be contacted, the CERT/CC typically discloses information publicly after 45 days since first contact attempt [23].

Software vulnerabilities coordinated by the CERT/CC may come from internal research or from outside reporting. Vulnerabilities discovered by outside individuals or organizations may be reported to the CERT/CC. Depending on severity of the reported vulnerability, the CERT/CC may take further action to address the vulnerability and coordinate with the software vendor.

The CERT/CC coordinates information with US-CERT and other computer security incident response teams. In general, US-CERT handles cases that concern US national security, whereas CERT/CC handles more general cases, often internationally.

#### **1.3.2.5** National Vulnerability Database (NVD)

The NVD is a comprehensive cybersecurity vulnerability database that allows the tracking of vulnerability trends over time. This trending service allows users to assess changes in vulnerability discovery rates within specific products or within specific types of vulnerabilities. NVD data is represented using Security Content Automation Protocol (SCAP), a suite of specifications that standardize the format and nomenclature by which software flaw and security configuration information is communicated, both to machines and humans (see table below). The NVD includes databases of security configuration checklists for the National Checklist Program, listings of publicly known software flaws, product names, and impact metrics

As of the end of September 2018, the NVD contained the following resources:

- Over 115,111 vulnerability advisories, with an average of 70 new vulnerabilities added daily;

- 181 SCAP-expressed checklists across 120 platforms containing thousands of low-level security configuration checks that can be used by SCAP-validated security products to perform automated evaluations of the system state;

- 359 non-SCAP security checklists (e.g., English prose guidance and configuration scripts);

- 249 U.S. Computer Emergency Readiness Team (US-CERT) alerts; 4,480 US-CERT vulnerability summaries; and 10,286 SCAP machine-readable software flaw checks; and

- A product dictionary with over 166,000 operating system, application, and hardware name entries; and over 94,000 vulnerability advisories translated into Spanish.

NVD is hosted and maintained by the National Institute of Standards and Technology (NIST) and is sponsored by the Department of Homeland Security's US-CERT. The use of SCAP data by commercial security products, deployed in thousands of organizations worldwide, has extended NVD's effective reach. Increasing demand for NVD XML data feeds (i.e., mechanisms that provide updated data from data sources) and SCAP-expressed content from the NVD website demonstrates an increased adoption of SCAP.

In the past year, the NVD continued to see a significant upward trend in the number of vulnerabilities received. To support this increased workload, several strategies are in progress, including longer-term efforts to focus on vulnerability ontology and natural language processing to manage future growth. Overall, the NVD continues to experience an average download growth rate of over 10% per month.

A key component of the NVD is the Common Vulnerability Scoring System (CVSS), used for measuring the relative severity of software flaws. In 2017, the NVD began providing CVSS base scores following the CVSS v3 specification within the data feeds. Currently, NIST is working with the vulnerability community to enable the automated analysis of metrics, such as CVSS, establishing a baseline of the minimum information needed to properly inform the vulnerability management process, and facilitating the sharing of vulnerability information across language barriers. To assist in this work, a public draft of *NISTIR 8138, Vulnerability Description Ontology (VDO): A Framework for Characterizing Vulnerabilities*, was created to foster a conversation and collect feedback on the best mechanisms to improve the degree of automation within vulnerability management processes. In FY 2019, NIST is planning to develop the VDO iteratively through collaboration with the security automation community on GitHub. This approach will allow participation from as many stakeholders in the vulnerability community as possible.

| SPECIFICATIONS                                              | DESCRIPTION                                                                                                                                        |  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Languages                                                   |                                                                                                                                                    |  |

| Extensible Configuration Checklist                          | Used for authoring security                                                                                                                        |  |

| Description Format (XCCDF) 1.2                              | checklists/benchmarks and for reporting the results of evaluating them                                                                             |  |

| Open Vulnerability and Assessment<br>Language (OVAL) 5.11.2 | Used for representing system-configuration<br>information, assessing machine state, and<br>reporting assessment results                            |  |

| Open Checklist Interactive Language<br>(OCIL) 2.0           | Used for representing checks that collect<br>information from people or from existing data<br>stores populated by other data collection<br>methods |  |

| Reporting Formats                                           |                                                                                                                                                    |  |

| Asset Reporting Format (ARF) 1.1                            | Used to express information about assets and to define the relationships between assets and reports                                                |  |

#### **Table 1.1: SCAP 1.3 Specifications**

| Asset Identification 1.1                 | Used to uniquely identify assets based on     |  |

|------------------------------------------|-----------------------------------------------|--|

| 1 isset identification 1.1               | known identifiers and other asset information |  |

|                                          | known identifiers and other asset information |  |

| Identification Schemes                   |                                               |  |

| Common Platform Enumeration (CPE) 2.3    | A nomenclature and dictionary of hardware,    |  |

|                                          | operating systems, and applications; a method |  |

|                                          | to identify the applicability to platforms    |  |

| Software Identification (SWID) Tags 2015 | A structured metadata format for describing a |  |

|                                          | released software product                     |  |

| Common Configuration Enumeration         | A nomenclature and dictionary of software-    |  |

| (CCE) 5                                  | security configurations                       |  |

| Common Vulnerabilities and Exposures     | A nomenclature and dictionary of security-    |  |

| (CVE)                                    | related software flaws                        |  |

| Measurement and Scoring Systems          |                                               |  |

| Common Vulnerability Scoring System      | Used for measuring the relative severity of   |  |

| (CVSS) 3                                 | software flaws                                |  |

| Common Configuration Scoring System      | Used for measuring the relative severity of   |  |

| (CCSS) 1.0                               | device security (mis-)configuration issues    |  |

| Content and Result Integrity             |                                               |  |

| Trust Model for Security Automation Data | Guidance for using digital signatures in a    |  |

| (TMSAD) 1.0                              | common trust model applied to security        |  |

|                                          | automation specifications                     |  |

#### 1.3.2.6 Trust-Hub

Trust-hub is a web portal (available at <u>www.trust-hub.org</u>) for the hardware security community to exchange of ideas, benchmarks, platforms, tools, and educational resources, which is led by the University of Florida and has been supported by funds from the National Science Foundation (NSF) for the last eight years. In 2018, Trust-hub has added a Vulnerability Database sub-portal, which currently consists of (1) a physical attack taxonomy that highlights the mechanisms used by attackers in IC/PCB reverse engineering, hardware Trojan insertion, fault injection, side channel analysis, etc.; and (2) a list of academic and commercial computer aided design (CAD) tools available for protecting hardware IP and assessing system-on-chip (SoC) susceptibility to information leakage, hardware Trojans, side channel attacks, fault injection, and probing.

While this sub-portal is a promising joint initiative from academia and industry that aligns well with the goals outlined in this document, it remains a work-in-progress. An additional SoC vulnerability database is mentioned as "coming soon". The physical attack taxonomy only includes attacks categorized in one manner. Further, it can be improved by adding short descriptions, execution steps, consequences, and details about the time, skills, and resources required for each attack. The CAD tool list provides just the right amount of information about each tool, but it's not yet exhaustive. Researchers and vendors are encouraged to send details to the Trust-hub Vulnerability Database organizers to gain exposure for their tools and so that community has a better idea of which tools still need to be developed.

#### **1.3.2.7 Trusted Silicon Stratus**

The Nimbis Services Trusted Silicon Stratus (TSS) Supply Chain Risk Management (SCRM) Cloud, is a secure cloud service for government agencies to design integrated circuits (ICs) in a

private community cloud. This novel cloud service will be the first authorized-to-operate (ATO) multi-tenancy, inter-organizational, collaborative, trusted microelectronics (i.e., ASICs, FPGAs, and SoCs) SCRM ecosystem that provisions a design-to-release, manufacturing-to-operational, Life-Cycle-Management cloud computing infrastructure and enterprise architecture. A novel ecosystem for EDA software, IC design, and manufacturer data has been implemented as a private community cloud computing workflow-as-a-service (WFaaS) for DoD research and development teams, contractors, and government research laboratories.

The TSS offers a secure user configurable Trusted Microelectronics chip design ecosystem hosted on Amazon.GOV. This cloud-based service enables the affordable multi-organizational chip design and verification platform required for today's complex microelectronics development cycle. The TSS provides:

- EDA Tools

- Scalable Computing Resources

- Life Cycle Management

- PDK & IP Libraries

- Metered Billing

- Tiered levels of security

- Archiving and version control

#### **1.3.3 Hardware Differentiation**

#### **1.3.3.1** Overview of Hardware Security Taxonomies

As described above, there are several description frameworks available for characterizing computer vulnerabilities in the form of the CVE ecosystem (CVE, CVSS, CWE, CWSS, and CAPEC). CVE and CVSS have been used by the community to document well known vulnerabilities such as Spectre/Meltdown and Rowhammer on the NVD. All of the CVE ecosystem is capable of usefully characterizing hardware vulnerabilities. However, CWE and CAPEC often lack key hardware weakness concepts and hardware specific attacks.

Outside of the CVE ecosystem, there have been several efforts to create more detailed taxonomies for particular domains of hardware vulnerabilities. Taxonomies of hardware attacks and attackers have a long history [24], [25]. The most well-known current effort is Trust-Hub, (described in section 3.2.7) which contains taxonomies of physical vulnerabilities, hardware trojans, and hardware obfuscation. Guin, DiMase, and Tehranipoor [26], have also published a taxonomy of counterfeit ICs. There have been a variety of specialized taxonomies around specific weaknesses including a taxonomy of attacks based on speculative execution (e.g. Spectre/Meltdown) [27], general fault attacks [28], differential power analysis [29], and injection attacks [30] to name a few (see Table 2). In aggregate, these taxonomies give a detailed picture of the world of hardware security. However, with a few exceptions [31], the focus is on the definition of concepts for attacks, weaknesses, and attackers. The attributes of these attacks are often missing that would allow modeling and the development of best practices around each kind of attack. For example, while optical fault injection (OFI) attacks are well studied, no description framework that we know of has included the concepts necessary to describe *when* an OFI attack would be successful on *what* device.

| Hardware Topic                   | Reference                           |

|----------------------------------|-------------------------------------|

| Physical Vulnerabilities         | Trust-Hub                           |

| Hardware Trojans                 | Trust-Hub                           |

| Obfuscation                      | Trust-Hub                           |

| Fault Attacks                    | Karaklajic et al. 2013 [28]         |

| Speculative Execution            | Canella et al. 2019 [27]            |

| Counterfeits                     | Guin et al. 2013 [26]               |

| Biased-Fault Attacks             | Farhardy et al. 2015 [32]           |

| DPA analysis and countermeasures | Marzouqi and Salah 2013 [29]        |

| Fault Injection and simulation   | Piscitelli [33]                     |

| Signal Injection Attacks         | Giechaskiel and Rasmussen 2019 [30] |

| Attackers                        | Anderson and Kuhn 1996 [24]         |

| Hardware attacks and attackers   | Rae and Wildman 2003 [34]           |

| Hardware attacks and attackers   | Keommerling and Kuhn 1999 [25]      |

| Smartcard                        | Yahay and Omar 2010 [31]            |

#### Table 1.2: Examples of hardware security taxonomies

#### 1.3.3.2 Hardware Weakness and Attack Pattern Descriptions

The concepts necessary to describe software weaknesses are well documented in the CWE description framework described in Section 3.2.2. In addition to software specific weaknesses, CWE includes many concepts required for computer security. Moreover, in addition to its taxonomies of concepts, it includes an ontology which allows for relations between those concepts and the concepts from CAPEC. This allows for the detailed description of hardware errors, even if hardware specific concepts are missing.

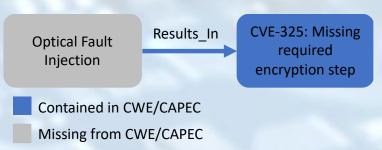

For example, the CWE concept "CWE-325: Missing Required Encryption Step<sup>4</sup>" is described as "The software does not implement a required step in a cryptographic algorithm, resulting in weaker encryption than advertised by that algorithm." While this effect could be caused by an inherent software weakness it is often the end result of hardware glitching attacks. The CWE ontology contains the relation "resultant" and CWE-325, in its definition, can be described by that relation. Thus CWE contains the concepts and relations to describe the action of a (for example) fault injection attack that causes an encryption algorithm to prematurely dump the plain text to a recoverable media.

CWE and CAPEC do not contain a concept for "Optical Fault Injection", though CAPEC does have a concept for "Fault Injection". From the hardware perspective, differentiating between types of fault injection is important since, for example, timing faults and optical faults will have wildly different mitigations. Many other notable attacks have no representative hardware concepts (e.g. Spectre/Meltdown, Rowhammer, power analysis etc.). However, as noted above, many of the key concepts have been described in some detail though the various taxonomic efforts over the past 20 years. A simple first step towards making the CVE ecosystem more

<sup>&</sup>lt;sup>4</sup> https://cwe.mitre.org/data/definitions/325.html

relevant to hardware would be the incorporation of existing taxonomic concepts (e.g. those of Trust-Hub) into CWE and CAPEC.

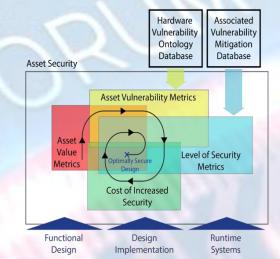

## 1.3.3.3 Hardware Security Estimation

Estimating the security and risk of

electronic devices is key to addressing hardware security concerns. They allow for a rational distribution of resources towards high impact security problems. Importantly, such estimations are necessary to incentivize the adoption of secure designs by industry. Security estimates must take several factors into account:

- Hardware security issues range from remotely accessible vulnerabilities such as Spectre/Meltdown, to counterfeit production, to subversion via fault injection. Generic security estimation is impossible and a threat model must be specified.

- Security estimates must take preventative measures into account such as secure designs, practices, and testing/verification.

- Hardware has a distinct and complex lifecycle beginning with multiple layers of design abstraction to fabrication and use in multiple environments.

- Hardware usually consists of integrated components beginning with integration of 3<sup>rd</sup> party IP at the level of IC design to printed circuit boards and large systems.

Indeed, integration poses an interesting problem for security estimation due to the combination of relatively secure components with other (possibly much less secure) components. This situation presents both risk and opportunity; restricting secure processes through trusted and secure components may allow for compensation for less secure components. However, an unsecure component may also serve as a "weakest link" for an otherwise secure system. Regardless, the ability to integrate security estimates across a system is essential to most applications.

#### **The Dimensions of Security Estimation**

There have been several approaches to establish measurements of security for microelectronics (see [35] for a review). Here we propose a trinary structure that roughly summarized security metrics:

- Error Metrics (Impact) For a given identified error in a device, what is the severity of that error in terms of its damage, its accessibility, and the ability to mitigate that error. Error metrics usually measure "impact".

- **Trust Metrics (Reliability)** An estimate as to whether the instantiated device is what you think it is in terms of design, production, chain of custody, and performance (to be free from defects). Trust metrics usually roughly measure the expected reliability of a device.

- Subversion Resistance (Effort) An estimation of how secure the device is against deliberate attack. This can be measure roughly in terms of the effort that must be expended by the attacker to subvert the device. Though "effort" may also represent access to devices, the cost of the equipment necessary to attack the device, computer cycles required to break an encryption algorithm, etc. [36]

These scoring domains cover separate but closely related security descriptions. Error Metrics describe a defect that has been discovered or theorized. Trust Metrics can be informed by libraries of known Errors and their structure. Similarly, known errors inform the subversion resistance of a particular device. For example, a processors' vulnerability to the various attacks on speculative processing must be taken into account when estimating the effort required to subvert the processor in an attack.

Trust metrics are closely related to but differ from subversion resistance. A device may have a high trust score in the sense that it has a well-documented manufacturing process, and performs to specifications. However, it may be vulnerable to side-channel attacks and therefore have a relatively low subversion resistance. Similarly, a low trust score (which may indicate that the device was tampered with at some point during manufacture) will also indicate a low security resistance since the device may be more likely to contain a leverageable trojan. Finally, a device may be hardened against attacks but the design may be overly complex causing unexpected errors. Thus, it may have a high subversion estimate but low trust estimation.

#### **Security Metrics in Hardware**

**Error Scoring:** The scoring of errors in software has been key for the functioning of the software vulnerability patching infrastructure including vulnerability disclosure and mitigation strategy. The key efforts have been the Common Vulnerability Scoring System (CVSS, described in section 1.3.2.5)<sup>5</sup> and the Common Weakness Scoring System (CWSS)<sup>6</sup>. The CWSS is integrated with the Common Weakness Enumeration (CWE) so it's focused on software "weaknesses" which may or may not yet have been instantiated in actual software. CWSS is a more flexible than CVSS, being more abstract. CWSS also is more amenable to interaction with the Common Attack Pattern Enumeration and Classification (CAPEC) ontology.

There is no vulnerability scoring framework (e.g., an equivalent to CVSS) specifically for hardware, though there have been proposals in that direction [35]. CVSS has been used to characterize the severity of many vulnerabilities and weaknesses discovered in hardware and reported in the NVD. However, unlike most software patches, the mitigation of hardware vulnerabilities is often partial in its effectiveness; the attack surface still exists but may require a infeasibly high amount of effort to subvert.

**Trust Metrics:** A great deal of thought has gone into the general problem of establishing metrics of trust for software. For example, see Table 1 from Alberts et al. (2012) [37] for some of the metrics designed for different parts of the software lifecycle. These metrics reflect both verification of the software, but also the soundness of design and manufacture procedures. In hardware, trust has often been associated with reliability and industry has already produced a wide variety of tools to help designers and manufacturers improve yield, functionality, and SWaP (Size, Weight and Power). Thus, one view of trust metrics for a given device is the coherent combination of the various testing regimes the device goes through during design, manufacture and insertion. While there have been efforts to combine metrics [35], so far there is no standardized way to fuse design scores for a given threat model.

<sup>&</sup>lt;sup>5</sup> https://www.first.org/cvss/specification-document

<sup>&</sup>lt;sup>6</sup> https://cwe.mitre.org/cwss/cwss\_v1.0.1.html

| Life cycle phase         | Example Security Measure                                                     |  |

|--------------------------|------------------------------------------------------------------------------|--|

| Requirements Engineering | Percent security principles in design                                        |  |

|                          | Percent security requirements subjected to analysis                          |  |

|                          | Percent of security requirements covered by attack patterns                  |  |

| Architecture and design  | Percent of design subject to attack surface measurement                      |  |

|                          | Percent of design components subject to risk analysis                        |  |

| Coding                   | • Percent of software components subject to static and dynamic code analysis |  |

| 2. 1. 2.                 | against known vulnerabilities and weaknesses                                 |  |

|                          | Percent of defects discovered during coding                                  |  |

|                          | Percent of components subject to code integrity and handling procedures      |  |

| Testing                  | Number of defects discovered during testing                                  |  |

|                          | Percent of components that demonstrate security requirements                 |  |

#### Table 1.3: Possible software security metrics from Alberts 2012

**Subversion Resistance:** Software vulnerabilities tend to be viewed as binary - they are either exploitable or patched. This differs from many hardware attack surfaces (e.g., side-channel analysis) which can often be mitigated but are still available for exploitation to sufficient effort and expertise. "Bit-Security" in encryption is a good example of a non-binary measure of subversion resistance. Bit-security of *n* generally mean  $2^n$  operations are required to break it. In the case of symmetric encryption this generally refers to the key length. Thus, AES symmetric encryption [38] with key length 128 also has bit-security of 128. Asymmetric public key encryption presents a different situation since there are always more efficient ways to attack an algorithm other than brute force methods. For example, 3072-bit RSA, which has key size of 3072, is estimated to have bit security of 128.

The problem of estimating the effort required to exploit a hardware vulnerability has been difficult and made assessing the effectiveness of hardware security features difficult. One approach for estimating subversion resistance is to appeal to "time to completion" approaches from project management. These can be used to produce a distribution of effort required for a successful attack [39]. Similarly, game theoretic approaches can be used to estimate the risk/benefits for attackers and defenders in an adversarial context [40].

**Vulnerabilities in multiple lifecycles, data types, and integrated systems:** The distinct lifecycle of hardware contains different phases at which vulnerabilities could be intentionally or unintentionally introduced. At the same time, these phases also present multiple data sources that can be used to provide assurance regarding security. For a given threat model, estimation of security may require a select set of data across different parts of the lifecycle. Hardware generally has a long (in the case of defense components a very long) life in comparison with software. Therefore, the use of a design may differ significantly in its later deployment than for what it was first intended.

#### **1.3.3.4 Vulnerability Disclosure**

Once a vulnerability in a public system has been discovered, the question is how to best alert relevant parties to produce a mitigation for that vulnerability before it can be exploited. When the vulnerability is discovered within the organization that produces a product, often the patch is developed and distributed without any public acknowledgement of the vulnerability. However, even internally discovered vulnerabilities are often given CVEs and publicly acknowledged.

Most cases of vulnerability disclosure arise when a 3<sup>rd</sup> party discovers the vulnerability. Then the reporting party must decide on how to proceed and whether to alert the product manufacturer or to disclose the vulnerability without input of the vendor (e.g. public disclosure). In the past, vulnerability disclosure was an extremely sensitive process with reporters being concerned about lawsuits brought by vendors.

In software, a formal vulnerability disclosure process has been largely recognized to be a benefit to both vendor and reporter [42]. This is not to say that disclosure is uncontroversial or without problems. The case has been made that disclosing vulnerabilities provides attackers with both a training ground and ammunition [19]. Moreover, due to the prestige associated with discovering major vulnerabilities, the exploitability of vulnerabilities can be exaggerated, and in some cases reported vulnerabilities turn out not to be true [43]. However, without a disclosure process, users may be unaware of unpatched vulnerabilities within their system. This not only puts them at risk, but any network into which they have privilege, as well as making them a target for botnet recruitment. Lack of disclosure also leaves system integrators at risk, as well as those who may use software without acknowledgement (often as a legally questionable practice). Several best practices have been published and collated in ISO/IEC report 29147 on Vulnerability Disclosure and the related report 30111 on Vulnerability handling.

Vulnerability disclosure can take one of several routes. The vender may discover the vulnerability and handle the disclosure and mitigation completely independently. A non-vender party may discover the vulnerability and report it to the vendor, who then handles the mitigation and disclosure independently. The discover may disclose the vulnerability without consulting the vender. Finally, the vender, discoverer and other stake holders may work together in mitigation and disclosure of the vulnerability in a process usually referred to as "Coordinated Disclosure". Coordinated disclosure is of particular interest to the hardware case. Hardware vulnerability mitigation, but also the original equipment manufacturers (OEMs) and their network or suppliers. Additionally, researchers who report a hardware vulnerability often have already expended extensive effort to discover and characterize the vulnerability and would like to receive credit through publicity or other reward. The coordinated disclosure process allows the reporter to continue to participate in the disclosure process.

The mitigation of a hardware vulnerability mitigation often requires the coordination between three types of technical parties: (1) OEMs, which are the companies that brand and distribute the products in which a vulnerability may occur, but might not manufacture all (or even most) of the component parts; (2) Hardware vendors manufacture the components but may have limited understanding of the larger functioning of the integrated product; and (3) Software distributers produce the operating systems (and often firmware) that utilize the device, and as such, they play a primary role in developing and testing software based mitigations. Because the process involves a continued coordination between the reporter, vendor, and mitigators it may be advantageous to involve a "coordinator" party. This may be a governmental entity (e.g., US CERT), and a commercial entity (bug bounty or commercial brokers), or other entities. CMU-CERT has a recent extensive report on coordinated disclosure [42]

IoT devices have been a focus for future disclosure policy. Although they may be in hard to reach places and nonstandard environments making updates or replacement difficult, they also play a role in safety-impacting systems. The constrained nature of IoT devices (sensors, programmable logic controllers, low power chips, embedded controllers, limited battery life, etc.) limit the inclusion of sophisticated security and the mitigation of discovered vulnerabilities. On the other hand, the devices (especially infrastructure supporting devices) have life expectancies of years or even decades. Finally, for smaller disposable devices sophisticated security features may be cost prohibitive.

Thus vulnerabilities or weaknesses discovered in IoT devices can carry large risks but at the same time may be difficult patch. This difficulty makes the treatment of vulnerabilities sensitive, and require a careful disclosure process. Unfortunately, many (even larger) IoT dependent companies do not have a defined vulnerability disclosure policies. A survey by the Internet of Things Security Foundation found that companies with IoT products showed that only 10% had any official disclosure policy. Out of this 10%, the actual disclosure policy varied radically:

- 41.9% disclosure policies gave no indication of the expected disclosure timeline.

- 0.9% disclosure policies had a hard deadline of 90 days for fixes to reported issues.

- 46.9% of policies also had a bug bounty program. Two of these programs were however by invitation only, so were not open for general contribution.

- 78.1% of policies supplied researchers with a public key for encryption to protect their communications and report details.

- 18.8% of policies utilized a proxy disclosure service (e.g., bugcrowd.com)

#### 1.3.3.5 Summary of Gaps in the Hardware Vulnerability Description and Reporting Framework

**Identification of vulnerabilities:** CVE has been used successfully to identify and report hardware vulnerabilities in the NVD.

**Description framework for weaknesses and attack patterns:** The CWE and CAPEC description frameworks contain much of the necessary structure to describe hardware vulnerabilities. However, many hardware specific concepts are missing and those that do exist are at too high of a level to be useful (e.g., "fault injection"). Simultaneously, there have been many efforts to create taxonomies for hardware weaknesses and security issues. The inclusion of some of these into CVE and CAPEC could greatly extend their ability to describe hardware vulnerabilities adequately. On the other hand, very little has been done to systematically characterize hardware physical processes that would allow for detailed descriptions of weaknesses. This sort of detailed description framework would allow for the development of shard practices within the industry as a whole, as well within specific supply chains.

**Scoring and hardware security estimates:** Metrics for estimating hardware security appears to be a point of greatest differentiation between the software and hardware ecosystems. Scoring hardware vulnerabilities and weaknesses differ from software in three key ways. First, unlike most software vulnerabilities, many hardware vulnerabilities are not patchable. Second, if they can be mitigated, the mitigation is often partial – the attack surface persists though may

implausible to exploit. Third, because the attack surfaces persist, measuring the effort to subvert the device through these attack surfaces is a key metric. Finally, metrics that are robust to fusion across the lifecycle of the device and integration into higher level systems is key for useful risk estimates. These differences have further impacts in how hardware security metrics need developed:

- Any estimate needs to have a **defined threat model** (e.g. trojan, reverse engineering, remote activation, etc.) This is key for establishing what data from which parts of the lifecycle are relevant.

- Because hardware vulnerabilities are not patchable and persist in larger systems, there

must be some way of combining security estimates across the lifecycle of a device. A

system for countering fault injection may actually induce a different vulnerability [41].

Similarly, an emphasis on reduced accessibility during development may lead to a lack of

robustness in a device when it is deployed. A lack of awareness of this sort of tradeoff

will induce new weakest leaks in security development.

- The security estimates must be **comparable and integrable**. This is especially key for preventing weakest links in integrated systems. For example, a device may be secure for a copy machine but in a company network that device may form the weakest link and allow subversion the larger system.

- How **confident are we in our estimate**? A score of any kind by itself is insufficient. We need to have a methodology of assessing confidence in this score and how to improve the score [26]. A given score may be fully achievable (i.e. a functional verification on a relatively small device). Understanding the coverage of a given approach, and therefore our confidence in the result is essential. Finally, ideally a test framework could be established which allows automated data generation for increasing confidence. For example, as new Trojan models come to light, new tests can be generated to assure such an error is not present in already existing devices.

- There are two major perspectives to estimate risk in microelectronics. The first one is trust, that is the **risk that the component is already compromised**. This compromised state may be due to an unintentional error or defect, an intentional error (Trojan), or because the device is in fact a counterfeit. It is still important to think about the effort for an attacker to exploit this compromised state, however, the fundamental question is whether the device is and performs as expected. The second related estimate is the **effort of the attacker** to exploit a device. Indeed, with any device made by humankind, there is probably a way to exploit the device given enough resources. In the case of encryption, bit security has been a very good measure. However, many hardware security features need to be measured in expertise, person-hours/costly device time and accessibility. Effort required to compromise a device is of course closely related to whether the device is already compromised in terms of assurance; a device with a Trojan or known error with be easier to compromise.